# Design and Simulation of A Third Order MASH (1-2) Modulator for GSM Applications

#### Sabah A. Gitaffa

Sabahahg@yahoo.com

University of Technology

Department of Electrical Engineering

Hasan M. Azzawi

Eng.hasan.mahmood@gmail.com

University of Technology

Department of Electrical Engineering

**Abstract:** This paper presents a design and simulation of proposed MASH (Multi-stAge noiSe sHaping) modulator which can be used for GSM applications. MASH technique is chosen for GSM system, since low settling time, spurious level and phase noise can be obtained by using this technique. The phase noise obtained with this modulator is 30 dB if compared with other modulating techniques. Matlab (R2013a) is used for simulation of 3<sup>rd</sup> order, 32-bit digital MASH modulator.

Keywords: GSM, Analog-to-Digital Convertor (ADC), Quantization noise, MASH (multi-stage noise shaping), dither.

#### 1. Introduction

The GSM (global system for mobile communications), which originated from group special mobile developed by European Conference of Postal and Telecommunications Administrations (CEPT), has become the most popular standard for mobile communication all over the world, and analog-to-digital converters (ADCs) are one of the key modules in a GSM system [1]. Analog to digital converters are the interface between the real world which

is analog and the digital world where the information buried in signal is extracted, processed, and interpreted. In wireless communication systems for example having variety of services (i.e. voice, video, internet,...) on a single handheld cell phone requires large signal bandwidth to transfer higher data rates and providing these services inside a hostile metropolitan area means higher resolution (dynamic range) for ADCs. ADCs, therefore, are becoming more demanding in resolution and speed. As the battery life time for the portable devices is also a crucial factor, all of these should be achieved with low power consumption. Among different techniques of analog to digital conversion, oversampling deltasigma ADCs has found their place in many applications. Although these converters are originally used for high resolution low to medium speed applications such as audio and sensors, but many work has been done in recent years to improve their performance for higher speed applications. Wireless communication systems are particularly interested in delta-sigma ADCs that can accomplish analog to digital conversion with much lower power compared to Nyquist rate ADCs such as pipeline [2].

# 2. System Architecture

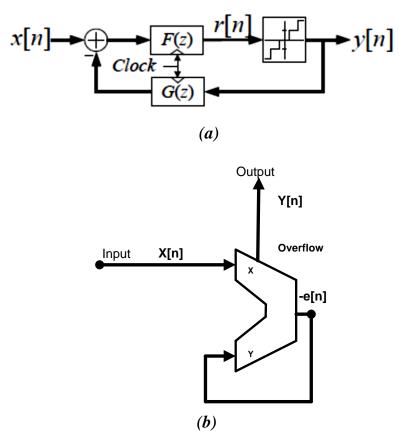

Figure 1(a) shows the block diagram of a generic digital delta-sigma modulator and its block diagram as shown in fig. 1(b). It consists of a quantizer "forward transmission" and "feedback" filters, represented by their Z-transforms, F(z) and G(z) respectively. The input is a sequence of rational numbers, x[n],  $0 \le x[n] < 1$ , where n is a sample index. It is band-limited to  $B = [-\pi/R, \pi/R]$  where R is oversampling ratio. In practical implementations, it is common to represent the various sequences in the system in binary form. For example, it is assumed that x[n] is represented by a  $\rho$  bit binary number so, x[n] E  $\{0, 1, ..., 2^p-1\}/2^p$ . The system coarsely quantizes the input sequence, x[n], to a sequence of integer multiples of 1/M, namely v[n], where  $M = 2^Q$ , Q is a positive integer, and Q < p. The quantizer is assumed to be of the uniform mid-tread type whose operation is defined as [3]:

Figure (1): First order MASH Modulator (a) Block diagram, (b) digital MASH.

$$v[n] = \frac{1}{M} \left[ Mr[n] + \frac{1}{2} \right], \tag{1}$$

Where [x] is the largest integer less than or equal to x, and r[n] is the input to the quantizer as shown in the figure. The quantization error, q[n] is defined as,

$$q[n] = v[n] - r[n], \tag{2}$$

and it can be shown that:

$$q[n] = -\frac{2^{Q}}{2} + \frac{1}{2^{p}} \{0,1,...,K-1\}$$

(3)

Where:  $K=2^P/2^Q$ , i.e.  $-M/2 \le q[n] < M/2$ ., the range of v[n] is limited intentionally to  $\{V_{min},V_{max}\}$ , where  $0 < V_{min}$  and  $V_{max} < 1$  for practical reasons described later. When this happens, q[n] may not be bounded so, and the situation is referred to as "quantizer overload". It can be shown that:

$$v[n] = x[n] * st f[n] + q[n] * nt f[n],$$

$$(4)$$

Where: \* is the convolution operator, and  $st\ f[n]$  and  $nt\ f[n]$  are sequences whose Z-transforms are the so-called "signal" and "noise transfer functions" [3].

$$STF(z) = \frac{F(z)}{1 + F(z)G(z)},\tag{5}$$

and

$$NTF(z) = \frac{1}{1 + F(z)G(z)} \tag{6}$$

The filtered quantization error,  $e_{ds}[n]=q[n]*nt f[n]$  is called "shaped quantization noise" to distinguish it from the quantization error, q[n]. The filters, F(z) and G(z), are chosen such that NTF(z) suppresses the quantization error, q[n], within the input sequence's bandwidth, B. The most popular digital delta-sigma ADC, called the L<sup>th</sup> order delta-sigma ADC, and the output is:

$$F(z) = z^{-L} (1 - z^{-1})^{-L},$$

$$G(z) = (1 - z)^{L} - z^{L}$$

(7)

The signal and noise transfer functions are:

$$STF(z) = z^{-L}, NTF(z) = (1 - z^{-1})^{L}$$

(8)

Consequently, while the input sequence, x[n], is simply delayed by L samples, the shaped quantization noise, E[n], is attenuated within the signal band [3]. The resolution of modulator is given by [4]:

Resolution =

$$(SNR - 1.76)/6.02$$

(9)

The resolution is the number of steps the input range is divided into. It is usually expressed in bits (n) and the number of steps is expressed as 2 to the power n. With 12-bit resolution, for instance, the range is divided into  $2^{12}$ , or 4096, steps. The increase in the word length (in this work 32-bit) in the MASH distributes the quantization noise power over many more frequency components. Consequently, the measured spectrum is much smoother over the entire frequency range [5, 6].

### 3. Operation Technique

In this paper, we proposed a dither before each quantizer with third order noise shaping filter  $(1-Z^{-1})^3$  to improve the overall performance of system.

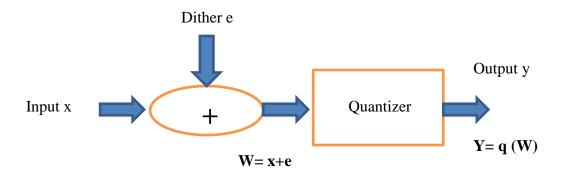

## 3.1 Dithering Technique

Dithering in oversampling analog-to-digital convertor is the act of adding a pseudo-random signal to the input of the quantizer (not to the modulator input) as shown in figure (2). The added random signal is white; it also becomes noise shaped like the quantization error so that the additional noise power in baseband is minimized. The aim of dithering is to effectively de-correlate and whiten the quantization error [7]. There exist two types of dither: subtractive-dithered (SD) and non-subtractive-dithered (NSD) systems. First, the dither signal must be available for subtraction at playback in subtractive-dithered systems, and so must the dither sequence or information be sufficient to be reconstructed, stored or transmitted with the signal. Second, the non-subtractive-dithered systems do not require this added information at playback. It is their primary advantage over subtractive-dithered systems. Practically speaking, it is difficult to use the first technique. One,

therefore, will proceed in our application with the technique of non-subtractive dither [8]. Quantization can introduce an error signal which is simply the difference between the output of the quantizer, q(x) and its input, x:

$$e = x - q(x) \tag{10}$$

The signal x is supposed to be a stochastic variable with density of Probability  $P_x(x)$  and a function characteristic  $P_x$ . Error will be uniformly distributed for arbitrary input distributions if and only if:

$$P_{x}\left(\frac{k}{q}\right) = 0\tag{11}$$

where k is an integer  $\neq 0$ . The idea consists then in adding to the signal a non-subtractive dither e with probability density  $P_e$  independent of the signal input x before the entry of the quantizer of the sigma-delta modulator. The quantizer output in a non-subtractive dithered quantizing system is given by:

$$w = q(x+e) \tag{12}$$

so that the total error is:

$$\varepsilon = x - q(x + e) \tag{13}$$

If the two uniformly distributed dither signals  $e_1$  and  $e_2$ , where  $e_1$  and  $e_2$  are noise errors from first stage and second stage respectively, adding them together creates a new dither signal whose PDF (Probability Density Function) is the convolution of two rectangles. This kind of dither is of very great practical interest. It meets the condition (2). Therefore; we will choose a triangular dither for our application. The triangular PDF distributed  $P_e$  is given by convolution of  $P_{e1}$  and  $P_{e2}$  where  $P_{e1}$  and  $P_{e2}$  are respectively the rectangular PDF distributed of  $e_1$  and  $e_2$ . The average and the variance of the quantification total error are

independent of the input signal of the quantizer using a non-subtractive dither [7].

Figure (2): Dither added to the quantizer input.

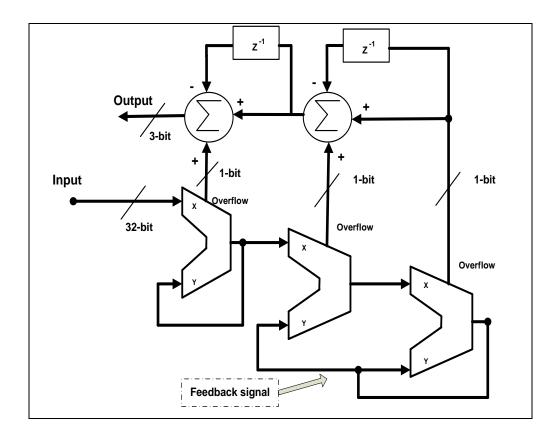

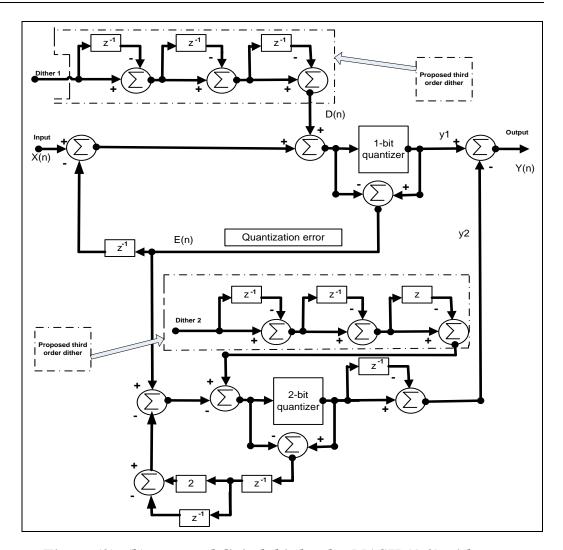

#### 3.2 Proposed MASH

The general structure of the conventional and proposed third order / three bit (1-2) Multi-stAge noiSe-sHaping (MASH) modulator is presented in Figure (3). As it can be seen, the feedback from the first stage output has been divided into two parts, the first part is the feedback from the output of the first quantizer and the second part is the input of the second stage. The output of the first stage of proposed system is:

$$y1 = X(n).Z^{-1} + D(n).(1-Z^{-1})^{3} + E_{1}(n).(1-Z^{-1})$$

(14)

Feeding the  $(E_1(n))$  of the first stage into the input of the second stage, the output of the second stage of proposed system is:

$$y2 = z^{-2}.(E_1(n) + D(n)) + (1 - z^{-1}).E_2(n)$$

(15)

Where  $E_2(n)$  is the quantization noise of the second stage. Combining the outputs of first and second stages, the final output of the proposed system is given by equation (14):

Output =

$$Z^{-3} . X(n) + D(n)(1 - Z^{-1})^{-3} + E_1(n)(1 - Z^{-1}) + E_2(n) . (1 - Z^{-1})^3$$

(16)

As equation (16) shows, the quantization noise of the system shifted out the band. This greatly improves the overall performance of the proposed system.

Figure (3): (a) Third order digital MASH without dithering

Figure (3):(b) proposed digital third order MASH (1-2) with dither.

#### 4. Simulation Results

For the simulation of proposed system, we developed MATLAB simulation program. The main program (mash12\_noise.m) is used to simulate the MASH with proposed dither. During the simulation, the main program loads the variables from files (dither1.MAT and dither2.MAT) respectively in to workspace. Several runs using PC Pentium 4 had been performed and the results are presented in Figures (4) and (5). Table (1) shows the basic requirement of the proposed system for uplink side.

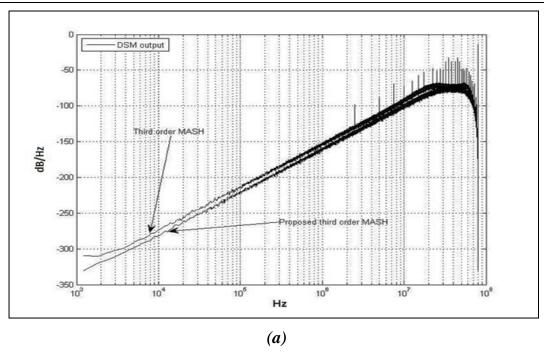

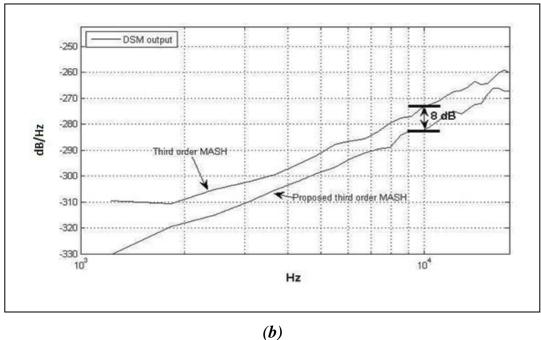

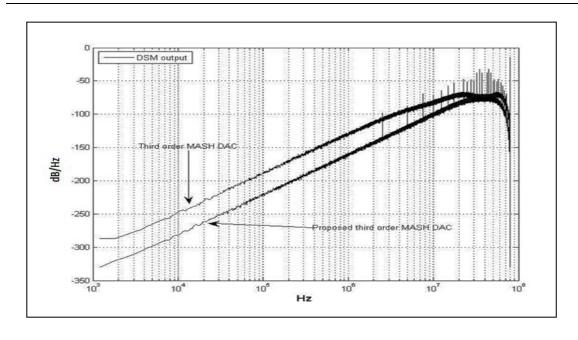

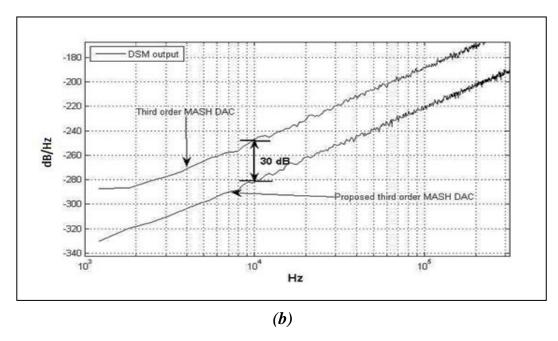

Figure (4) shows the enhancement in in-band quantization noise with first order noise shaping of dither noise. As can be seen, the total reduction in-band noise is 8 db if compared with the conventional third order (1-2) MASH and without dither. Figure (5) shows the final output noise reduction of the proposed system. The in-band noise reduction is 30 db with third order dither noise shaping  $(1-Z^{-1})^3$ .

In order to proof the strength of the proposed system, simulation results show an improvement of 250db in SNR at the output of the converter instead of 100 db was design in [9]. Table (2) summarizes the final simulation results of the proposed system compared with the system design in [9].

Table (1): Summarizes the System Requirements.

| Parameter             | Proposed system                 |  |

|-----------------------|---------------------------------|--|

| Order                 | third                           |  |

| Resolution            | 32-bit                          |  |

| Туре                  | MASH                            |  |

| Loop bandwidth        | 400KHz                          |  |

| Phase noise Reduction | 30dB In-band-quantization noise |  |

| Reference frequency   | 85MHz                           |  |

Table (2): Summarizes the simulation results.

| Parameter           | Proposed system            | Ref.[9]       |

|---------------------|----------------------------|---------------|

| Order               | Third                      | Fourth        |

| Resolution/SNR      | 32-bit/194 db <sup>‡</sup> | 15-bit/92 db* |

| Type                | MASH                       | Single Loop   |

| Loop bandwidth      | 400KHz                     | 100KHz        |

| Measured noise      | -225 @ 100KHz              | -140 @ 100KHz |

| Reference frequency | 85MHz                      | 11.23 KHz     |

<sup>\*</sup> By using equation (9).

Figure (4): Simulation showing enhancement in in-band quantization noise with first order noise shaping of dither noise, (a) noise shaping  $(1-Z^{-1})$ , (b) zoom-in.

(a)

Figure (5): Simulation showing enhancement in in-band quantization noise with third order noise shaping of dither noise, (a) noise shaping  $(1-Z^{-1})^3$ , (b) zoom-in.

#### 5. Conclusions

In this paper a third order modulator type 3-bit MASH (1-2) for GSM applications has been designed and simulated. The achieved results gives superior performance and suitable to GSM applications.

The quantization noise of proposed system is perfectly cancelled by using third order digital MASH (1-2) modulator (In-band noise reduction = -30 dB if compared with conventional third order MASH modulator).

#### References

- [1] Li Hongyi, etc., "An improved single-loop sigma-delta modulator for GSM applications", Journal of Semiconductors, Vol. 32, No. 9, September 2011.

- [2] Bahar Jalali Farahani, "Adaptive Digital Calibration Techniques For High Speed, High Resolution Sigma delta ADCs For Broadband Wireless Applications s", PhD thesis, The Ohio State University, 2005.

- [3] Sudhakar Pamarti," Quantization Noise Conditioning Techniques for Digital Delta-Sigma Modulators", Proceedings of the 19th International Symposium on Mathematical Theory of Networks and Systems (MTNS), 5–9 July, 2010.

- [4] Peter Kiss, "Adaptive Digital Compensation of Analog Circuit Imperfections for Cascaded Delta-Sigma Analog-to-Digital Converters", Ph.D. Thesis, Oregon State University, 1999.

- [5] Kaveh H. and Michael P. Kennedy, "Maximum Sequence Length MASH Digital Delta–Sigma Modulators", IEEE Transactions on Circuits and Systems—I: Regular Paper, Vol. 54, No. 12, December 2007.

- [6] Lieyi Fang, "A High-Speed, High-Resolution Sigma-Delta Modulator Analog-to-Digital Converter", PhD thesis, Texas Tech University, May 2004.

- [7] Mucahit Kozak and Izzet Kale, "Oversampled Delta-Sigma Modulators, Analysis, Applications and Novel Topologies", Kluwer Academic Publishers, 2003.

- [8] DADI Mohamed béchir1, etc.," New Approach to Optimize a Sigma Delta Modulator", International Journal of Computer Science and Network Security (IJCSNS), Vol.7 No.6, June 2007.

- [9] Li Hongyi, etc.,"An improved single-loop sigma-delta modulator for GSM applications", Journal of Semiconductors, Vol. 32, No. 9 September, 2011.

# تصميم و محاكاة مضمن الاشاره من نوع (Third Order MASH (1-2)) لمنظومة GSM

م. صباح عبد الحسن كطافة

Sabahahg@yahoo.com

الجامعة التكنولوجية - قسم الهندسة الكهربائية

م. حسن محمود عزاوي

Eng.hasan.mahmood@gmail.com الجامعة التكنو لوجية - قسم الهندسة الكهر بائية

#### المستخلص

هذا البحث يتضمن تصميم ومحاكاة مضمن مقترح لمنظومة GSM. تم اختيار تقنية مضمن من نوع (MASH) لمنظومة GSM، وذلك لتأمينها ضوضاء منخفضة وحزمة عريضة ودقة تفريق بالتردد عالية. النتائج التي تم الحصول عليها هي Matlab (R2013a) في محاكاة اذا ماتم مقارنتها بالتقنيات السابقة. تم أستخدام برنامج (Third order MASH / type (1-2)).

الكلمات الرئيسية: نظام جي أس ام، محول الاشارة الكمية الى الرقمية، الضوضاء التكمية، مضمن الاشارة من نوع ماش.